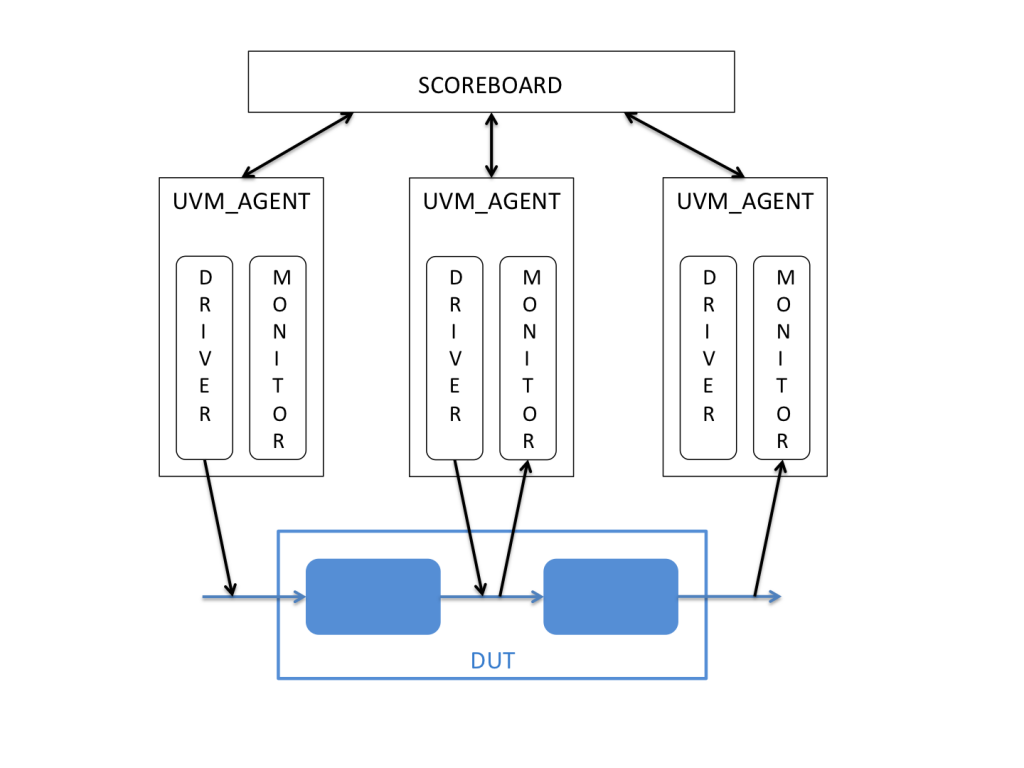

An UVM Verification Component (VC) can be used in multiple scenarios during verification. It usually consists of a driver and a monitor, thus allowing both stimulation of input signals and monitoring output signals. In some cases it might also replace a specific module inside the DUT to speed up simulation, e.g. modelling a high speed interfaces or bus master.

Transactions are abstracted to so-called sequence items and special analysis ports allow the use of scoreboards for the evaluation of transmitted or received transactions.

The following VCs are available. They can also be used with EVA.

Scalable Low-Voltage Signaling – Embedded Clock (SLVS-EC) Application Layer

- provides image data like it is transfered through an SLVS interface

- random image data or user provided data can be transmitted

MIPI CSI2

- Transmitter module for MIPI CSI2 interface

SPI

- Serial Peripheral Interface Master

AMBA APB

- Master and Slave functionality of the AMBA Advanced Peripheral Bus

AMBA AHB

- Master and Slave functionality of the AMBA Advanced High-performance Bus