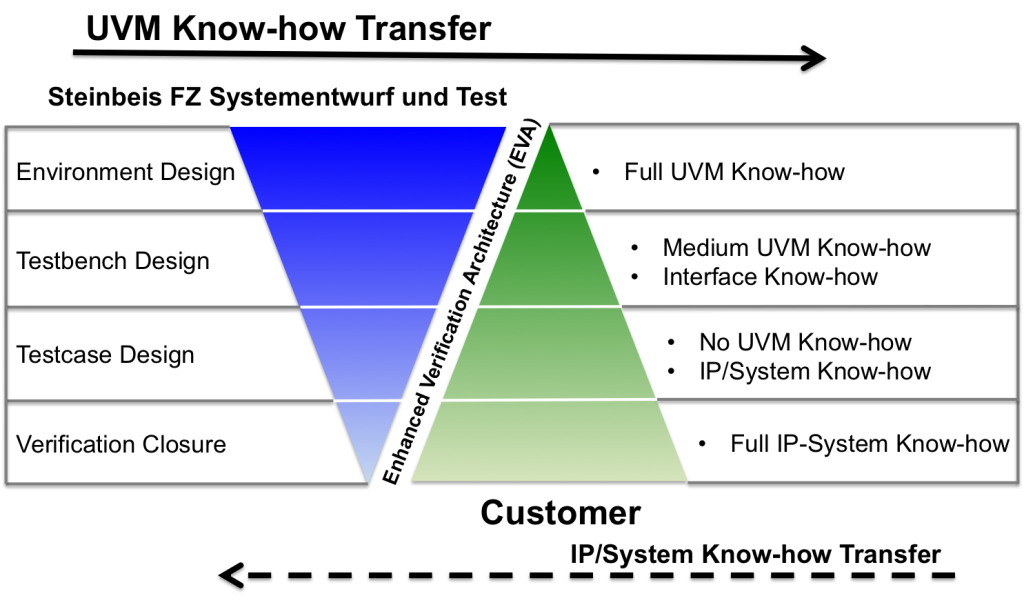

FPGA Designer-friendly solution for UVM Testbench Building

A step-by-step approach using our Enhanced Verification Architecture (EVA)

- Focus on reuse and flexibility, enabling quick bring-up of tests within a few days

- Step-by-step guidance towards the UVM (Universal Verification Methodology) Standard

- Well suited for complex FPGA VHDL designs (IP Blocks, Systems, SoCs)

- No object oriented SystemVerilog or UVM knowledge required to design TestBenches (TBs)

- Basic C/C++ knowledge needed only to write TestCases (TCs)

UVM provides a modular, reusable and interoperable standard framework, but to unleash its full power you will need to go through a steep learning curve. With our Enhanced Verification Architecture (EVA) the UVM environment details are abstracted away by inserting a layer between the testbench and the UVM library. Designers and Verifiers can fully focus on debugging, verification and writing testcases. You spend much less time on the verification environment with that approach.

We offer a Demo package for evaluation purposes which includes a free on-site walktrough of an example testbench.

Vertrieb durch:

TRIAS Mikroelektronik GmbH

UVM for complex FPGA Designs

www.trias-mikro.de