MIPI CSI2 Transmitter & Receiver

- Fully synthesizable IP core, designed for FPGA environments

- Up to 1600 Mb/s per lane (limited by FPGA capabilities)

- Internal operation with byte clock

- Fully compliant with the MIPI CSI-2 standard

- Meticom bridge ASIC to convert high speed LVDS into D-PHY compliant signals

- Supports 1-4 unidirectional data lanes

- User friendly interface

- Separate clock domains for application layer interface and CSI-2 output

- Automatic generation of CSI-2 synchronization packets (optional)

- Accepts pixel data in RGB, YUV, and RAW format with 6-14 bit per pixel

Configurable Image Processing Pipeline

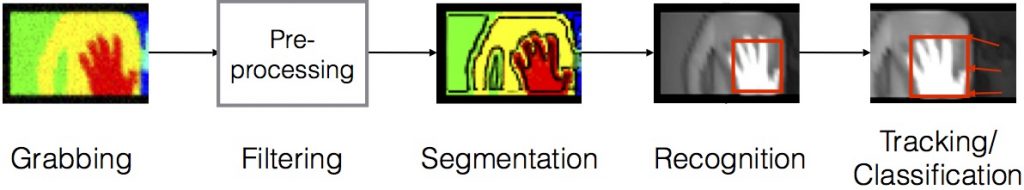

We offer a wide range of IP-Cores to leverage your smart embedded, power efficient and performant image processing application. A typical processing pipeline is build from consecutive steps as shown below:

Features of our solution:

- Grabber (to interface i.e. OmniVision7670)

- Color/Format conversion (RGB, YCbCr…)

- Up- and Downscaling

- Filtering (Subsample, PWL, Bayer2RGB, downshift)

- Object-Tracking (Camshift, Kalmanfilter, Particle Filter)

Circuit Debug&Test

JTAG Test Access Port (TAP) Controller

- Enables full Boundary Scan Test

- Enables parallel Memory BIST

- Compliant to IEEE 1149.1-2001

- EXTEST, BYPASS, SAMPLE/PRELOAD, INTEST, RUNBIST Instructions

- JEDEC identification code (IDCODE)

- ASIC proven

- freely definable Functional Test Pattern