- System architecture

- Preliminary studies (concept studies)

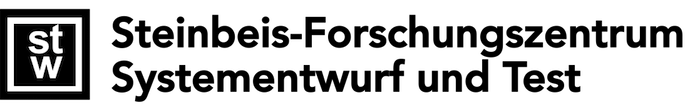

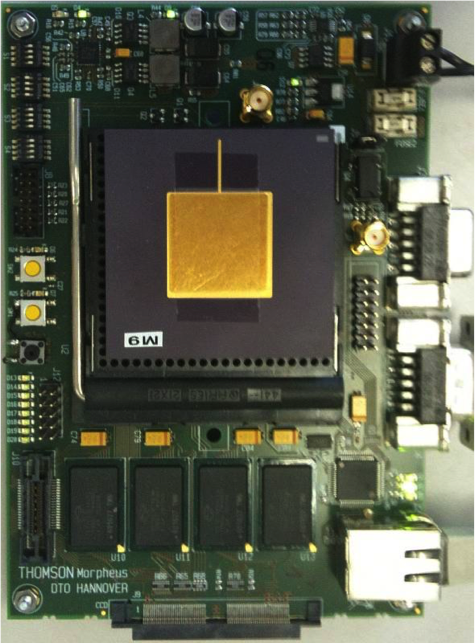

- FPGA/ASIC IP & SoC design (VHDL, Verilog, HLS)

- Extensive experience with Xilinx and Altera FPGA design flow

- Modeling (Matlab, Simulink)

- High-level Synthesis (CatapultC, Vivado, ImpulseC, C++/SystemC)

- ASIC/FPGA synthesis

- Code Rule Checking, syntax check (linting)

- Low power design, power requirements estimation

- Emulation and prototyping

- Equivalence checking

- Static timing analysis

- Design for test (DFT)

- Specification and documentation